重布线层(RDL):

自从NEC Electronics Corporation (现在的Renesas Electronics Corporation) 开发出 RDL-first 工艺以来,这一技术飞速发展并实 现了大量应用,例如 Amkor 公司在 2015 年和 2017 年开发的 SWIFTTM 和 SLIMTM 工艺。随后,台积电和三星 电机先后推出了 RDL-first 封装方案,并且向着板级和 2 μm 线宽线距工艺进发。长电科技于 2021 年 7 月在 国内率先推出了使用 RDL-first 形式的高密度扇出式 封装(XDFOITM-FcBGA-H),目前正处于快速追赶阶 段。由于具有更高的封装良率和布线密度,RDL-first 工艺更加适用于多芯片、大尺寸的高密度扇出封装, 例如处理器、存储芯片的封装等,随着 5G、人工智能等 技术的发展,其应用也更加广泛。

RDL(Re-Distribution Layer,重布线层)为先进封装的关键互连工艺之一,可将多个芯片集成到单个封装中。在介电层顶部创建图案化金属层的过程,将 IC 的输 入/输出(I/O)重新分配到新位置。新位置通常位于芯片边缘,可以使用标准表面贴装技术(SMT)将 IC 连接到印刷电路板(PCB)。RDL 技术使设计人员能够以紧凑 且高效的方式放置芯片,从而减少器件的整体占地面积。

晶圆级封装中RDL是最为关键的技术,通过RDL将IO端口进行扇入或者扇出;在2.5D封装中,通过RDL将网 络互联并分布到不同的位置,从而将硅基板上方芯片的Bump和基板下方的Bump连接;在3D 封装中,堆叠上 下是不同类型芯片时需要RDL重布线层将上下层芯片的IO进行对准,从而完成电气互联。

图1 重布线层(RDL)将 I/O 重新分配到芯片边缘

晶圆级金属重布线制程在 IC 上涂布一层绝缘保护层,再以曝光显影的方式定义 新的导线图案,然后利用电镀技术制作新的金属线路,以连接原来的芯片引脚和新 的凸点,达到芯片引脚重新分布的目的。重布线层的金属线路以电镀铜材料为主, 根据需要也可以在铜线路上镀镍金或者镍把金材料;相关核心设备包括光刻、电镀、 刻蚀及薄膜沉积等。

图2 重布线层(RDL)关键工序流程主要由十个步骤组成

RDL-first 工艺路线:

常见的 RDL-first 工艺路线共有三种,分别为:1) 使用物理气相沉积(PVD)制备介质层和 Cu 布线层, 并通过机械研磨除去载片;2)以玻璃载板为介质层,通 过电镀 + 刻蚀完成再布线层(RDL)布线,然后通过激 光解键合去除载片;3)将前两种方法混合使用,这种方法更适用于较为复杂的芯片结构。使用 PVD 进行 RDL-first 扇出的过程如图3 所示。首先使用 PVD 在 Si 片上形成 SiO2(或 SiN)薄层, 然后使用离子刻蚀(RIE)完成图形化,随后进行 Ti、Cu 溅射以及 Cu 沉积,接着通过化学机械抛光(CMP)工艺得到第一层与 Si 片相连的 RDL,重复以上步骤可 以得到更多的RDL。当所有RDL 制备完成后,通过底部凸块金属化(UBM)结构连接芯片,使用 PVD 完成的 RDL-first 工艺样品的切片扫描电子显微镜(SEM) 结果如图4所示。该方法使用的载板是Si 片,在上述步骤完成后还需通过机械研磨去除载板并在磨出的 焊盘上完成植球。这一工艺目前已较为成熟,但是对设备要求较高且造价高昂,因此已逐渐被第二种方案取代。

图3 使用 PVD 进行 RDL-first 扇出的过程

图4 使用PVD 完成的RDL-first 工艺样品的切片 SEM 结果

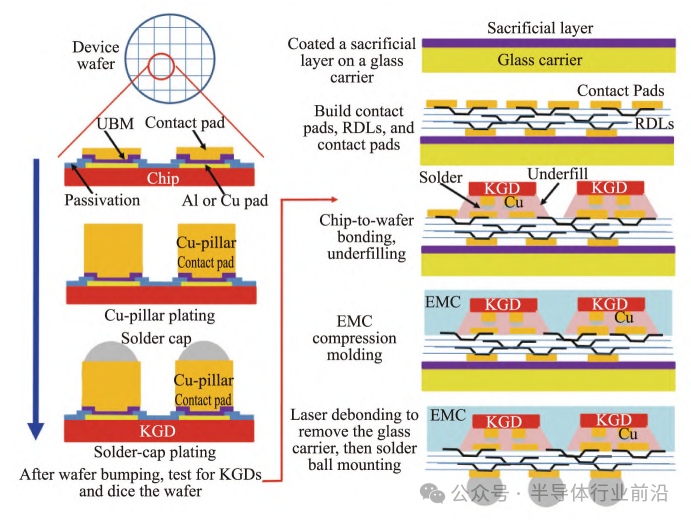

在玻璃载板上完成 RDL-first 工艺的关键步骤如图5所示。首先在玻璃载板上涂抹一层牺牲层(通常 使用激光释放材料),然后在牺牲层上完成 UBM 结构 和 RDL 的制备,接着在顶层进行芯片倒装、底填以及塑封等工艺,最后完成激光解键合和植球。这种方法较为简单,但是玻璃载板的引入提高了对封装过程中翘曲控制的要求。

图5 在玻璃载板上完成 RDL-first 工艺的关键步骤

第三种方法混合使用了前两种制备工艺。首先使 用第二种工艺,在玻璃载板上完成布线、UBM 结构制 备,随后将其键合到 Si 片上,去除玻璃载板后使用第 一种工艺的 PVD 和电镀技术继续布线,最后再进行芯 片倒装和塑封,通常可以实现六层以上的高密度布 线。混合 RDL-first 工艺的关键步骤如图6 所示,这一 工艺更适用于复杂的芯片结构,SPIL 和 Amkor 公司 都推出过使用这一工艺生产的产品。这种方案成本较高,目前主要应用于研发领域。

图6 混合 RDL-first 工艺的关键步骤

重布线层(RDL)在延伸和互连 XY 平面方面发挥关键作用。在扇入晶圆级封 装(FIWLP)和扇出晶圆级封装(FOWLP)等先进封装中,RDL 为核心关键工艺。使得封装厂能够在扇出封装技术方面与晶圆代工厂展开竞争。通过 RDL,IO Pad 可 以制成 FIWLP 或 FOWLP 中不同类型的晶圆级封装。在 FIWLP 中,凸块全部生长 在芯片上,芯片和焊盘之间的连接主要依靠 RDL 的金属线。封装后,IC 的尺寸几乎 与芯片面积相同。在 FOWLP 中,凸块可以生长在芯片外,封装后的 IC 比芯片面积 大(1.2 倍)。以 2.5D 先进封装的代表台积电的 InFO 为例,InFO 在载体上使用一个或多个裸 芯片,然后将其嵌入到模塑料的重构晶圆中。并在晶圆上制造 RDL 互连和介电层, 这是“芯片优先”的工艺流程。单芯片 InFO 提供高凸点数量,RDL 线从芯片区域 向外延伸,形成“扇出”拓扑。

图7 FAN IN 和 FAN OUT 型 RDL 工艺

图8 RDL 在台积电 InFO_OS 技术中为核心关键

地址:珠海市横琴新区荣珠道191号写字楼2106房

中国河南省洛阳市宜阳产业集聚区电子电器工业园1号

电话: 0756-6831190

0379-68950718

手机:13333896565(微信同号)

13532262175(微信同号)

邮箱:caojiangwei@jinnho.com

tristawang@jinnhoo.com

0379-68950718

+8613333896565

+8613532262175